|           | · <u></u>  |        |        |        |     | 1    |       | - |  |

|-----------|------------|--------|--------|--------|-----|------|-------|---|--|

| Name an a | pplication | of dem | ultipl | exers. |     | e e  |       |   |  |

| How man   |            | lines  | are    | needed | for | a 16 | input | : |  |

In this lab exercise you will begin your study of MSI circuits. In this lab exercise you will also study the 4-line to 10-line decoder. This circuit is often used as a BCD to decimal decoder. It can also be used as a decoder for any number of binary inputs less than four such as 3-line to 8-line decoders and 2-line to 4-line decoders.

LAB EXERCISE 9.1 Decoders Objectives

LD-2 Logic Designer

**Materials**

74LS42 4-Line to 10-Line Decoder

Jumper Wires

TTL Data Book

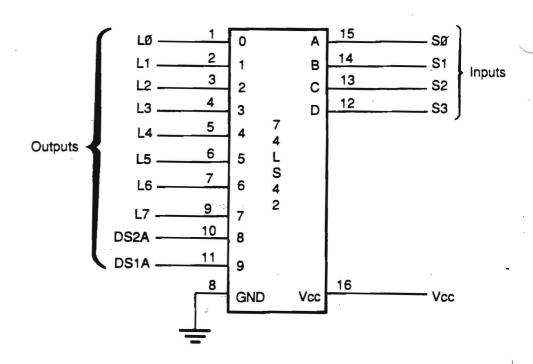

1. Wire DS1 DE and DS2 DE to 5 VDC. Now wire the circuit shown in Figure 9-12. This is the circuit for a BCD/DEC decoder.

**Procedure**

FIGURE 9-12. BCD/DEC Decoder.

- 2. Place S0-S4 to LO. Turn on power. D1 and L1-L7 should light. DS1 and DS2 should show a count of 1.

- Use S0-S3 as binary inputs. The LEDs L0-L7 are the decoded decimal outputs 0-7. DS2 is the 8 output and DS1 is the 9 output. Observe the circuit's operation and record your observations.

- 4. Now use S0-S2 as inputs and L0-L7 as the decoded outputs. This circuit is a 3-line to 8-line decoder.

- 5. Leave this circuit connected while you answer the following questions.

## Questions

1. What happens to the outputs when a count greater than nine is entered onto the binary input lines?

| 100                 | pe of circu                 | f 5     | -       |          | e to d |

|---------------------|-----------------------------|---------|---------|----------|--------|

|                     |                             | 1 -14   |         |          |        |

|                     |                             | 3       | 3.      |          |        |

|                     |                             |         |         |          |        |

|                     | -2 has an                   | 20000   |         | driver s |        |

| outputs<br>directly | connected L<br>ndicator dir | ED. Car | the 74L |          | ed to  |

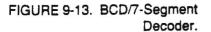

In this lab exercise you will investigate the use of the 7447 BCD-TO-SEVEN-SEGMENT DECODERS/DRIVERS. You will also learn about the use of seven-segment displays. You will study implementing simple displays.

LAB EXERCISE 9.2 Decoder/Drivers Objectives

**Materials**

LD-2 Logic Designer

7447 BCD-TO-7-Segment Decoders/Drivers

TTL 312 Common-Anode 7-Segment Display

Jumper Wires

#### 330 Ohm Resistors (7)

#### TTL Data Book

## **Procedure**

- 1. You will study the seven-segment LED display in the first part of this lab. Place the TTL 312 onto the LD-s breadboard.

- 2. Wire pin 14 to +5 VDC. Connect one end of a 330 ohm to ground and use the other end to determine and record the basing diagram for the TTL 312. No connection is made for pins 4,5 and 12. Notice that the TTL 312 is a common anode display and that 7-segment displays are also available in a common cathode configuration. that the display segments are labeled clock-wise from the top as a-f. The seventh segment is labeled as g and is the cross segment. Many of these displays have left and right decimal points. Some have the ability to display a leading minus sign. Seven-segment displays are often used to form small arrays of decimal digits. The display implemented here is a single digit decimal display. A full digit decimal display can display any number 0-9. A halfdigit can only display a blank or a one. Simple sevensegment displays can be made using LCD technology as well as LED technology.

- 4. Turn S0-S3 to LO. D1 should light and a zero should be shown in the 7-segment display. Use S0-S3 as the A-D inputs and the display as the output. Observe and record the operation of this circuit. Compare this display circuit to the one used on the LD-2 and note differences.

- 5. Leave this circuit connected while you answer the following questions.

1. Is the display clear? How could this be improved? Questions

2. What is the purpose of the 330 ohm resistors?

- 3. What count is displayed when the TTL 312 consumes the greatest power?

- 4. What input is required to blank the display?

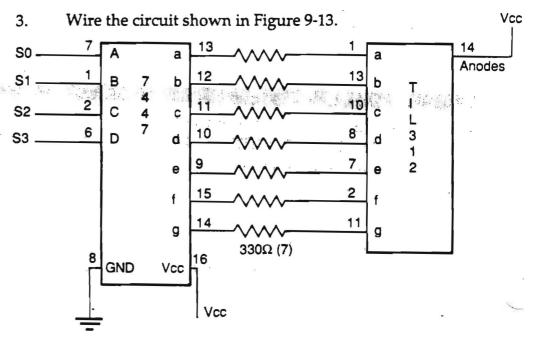

The purpose of this lab exercise is to investigate encoders. You will study the 74LS148 eight-line-to-three-line encoder. This type of encoder is also known as an octal encoder. It could be used to encode an octal keypad or to convert octal to binary.

LAB EXERCISE 9.3 Encoders Objectives

LD-2 Logic Designer

**Materials**

74LS148 8-Line to 3-Line Priority Encoder

## Jumper Wires

## TTL Data Book

## **Procedure**

- 1. Place the 74LS148 onto the LD-2 breadboard. Connect power and ground to the 74LS148.

- 2. Wire the circuit shown in Figure 9-14. This is the 8-line to 3-line encoder.

FIGURE 9-14. 8-Line to 3-Line Encoder.

- 3. Place S0-S7 to HI. Turn on power. D1 and L0-L2 will light.

- 4. Use S0-S7 as inputs and L0-L3 and L7 as outputs. Observe and record the operation of this circuit. Pay attention to what happens when more than one input is LO.

- 5. Leave this circuit connected and answer the following questions.

# Questions

1. Are the inputs to the 74LS148 LO true or HI true?

| Explain what is meant by a priority encoder? |

|----------------------------------------------|

|                                              |

|                                              |

In this lab exercise you will study digital multiplexers. The 74LS153 4-line to 1-line data selector/ multiplexer will be studied. A multiplexer can be used as a data selector or for parallel to serial conversion. A multiplexer can also be used to implement logic functions. The following lab exercise will familiarize you with the operation of the 4-line to 1-line multiplexer.

# LAB EXERCISE 9.4 Digital Multiplexers

LD-2 Logic Designer

Materials

**Objectives**

74LS153 4-Line to 1-Line Data Selectors/Multiplexers

Jumper Wires

TTL Data Book

- 1. Place the 74LS153 on the LD-2 breadboard. Wire power and ground to the circuit.

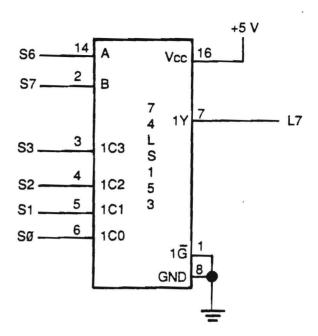

- 2. Wire the circuit shown in Figure 9-15. This circuit is a simple multiplexer.

FIGURE 9-15. Simple Multiplexer.

- 3. Place S0-S3, S6 and S7 to LO. Turn on power. D1 should light.

- 4. Use S0-S3 as the data inputs, S6 and S7 as the select inputs and L7 as the output. Observe and record the operation of this circuit.

- 5. In this part of the experiment you will use the 74153 to implement a logic function. You will implement the logical AND function. To do this place S3 to HI and S0-S2 to LO.

- 6. Use S6 and S7 as the A and B inputs and observe the output on L7. Verify the truth table for this circuit.

- 7. Leave this circuit connected while you answer the following questions.

| Questions | Explain the operation of the 4-line to 1-line multiplexer. |

|-----------|------------------------------------------------------------|

|           |                                                            |

|           |                                                            |

2. How would you implement the logical EXNOR using a 74LS153?

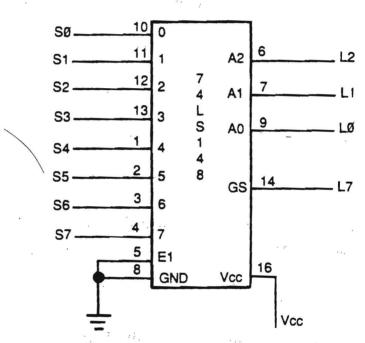

In this lab exercise you will study demultiplexers. Demultiplexers or data distributors are used extensively in digital computers. You will study the 74LS138 3-line to 8-line decoders/demultiplexers. This can be used as an address decoder for memory circuits or as a demultiplexer.

LAB EXERCISE 9.5 Demultiplexers

**Objectives**

**Materials**

LD-2 Logic Designer

74LS138 3-Line to 8-Line Decoders/Demultiplexers

Jumper Wires

TTL Data Book

- 1. Place the 74LS138 on the LD-2 breadboard. Wire power **Pr** and ground to this circuit.

- 2. Wire the simple demultiplexer circuit shown in Figure 9-16.

Procedure

FIGURE 9-16. Simple Demultiplexer.

| This circuit is a basic decoder circuit with additional gating |

|----------------------------------------------------------------|

| for enabling the circuitry. Any decoder with one or more       |

| enable inputs can be used as a demultiplexer. Use S0- S2       |

| as the select inputs, S7 as the data input and L0-L7 as the    |

| outputs. Observe the circuit operation and record your         |

| observations. Pay attention to the state of unselected         |

| outputs.                                                       |

|                                                                |

| 4. | Leave this | circuit   | assembled                               | as | you | answer | the | following |

|----|------------|-----------|-----------------------------------------|----|-----|--------|-----|-----------|

|    | questions. | V (11 × 1 | y v v v v v v v v v v v v v v v v v v v |    |     | on     |     | 2.0       |

|   |     | -   | - | - |   |

|---|-----|-----|---|---|---|

|   | 118 |     |   |   | • |

| - | 40  | sti | • |   | • |

| 1. | Since the demultip   | lexer | is the in | verse | funct | ion o | of the | 'is |

|----|----------------------|-------|-----------|-------|-------|-------|--------|-----|

|    | multiplexer, could   | the   | 74LS138   | be    | used  | for   | serial | to  |

|    | parallel conversion? | ?     | 2         |       |       |       | r      | ê   |

| 2. | What type of circuit is a demultiplexer made from? |

|----|----------------------------------------------------|

|    |                                                    |